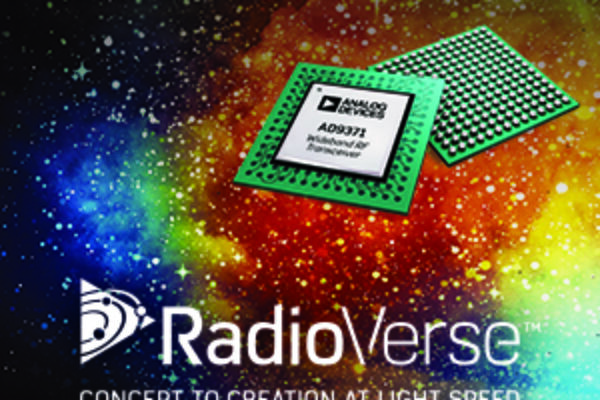

Microsemi PolarFire FPGAs talk to ADI’s wideband RF transceiver chip

Designers working with the AD9371—which offers dual channel transmitters and receivers, integrated synthesizers and digital signal processing functions—can employ PolarFire FPGAs to interface and interoperate with JESD204B, achieving lower power implementation than competing devices.

PolarFire FPGAs feature a 12.7 Gbps transceiver fully optimized to be area efficient and low power, resulting in total power of less than 90 mWs at 10 Gbps. Its intellectual property (IP) cores, which implement the transmitter and receiver interfaces of the JESD204B standard, integrate with JESD204B-based data converters. They support link widths from x1 to x8, and link rates from 250 Mbps to 12.5 Gbps per lane using subclass 0, 1 and 2. Interoperability with the AD9371 RF transceiver makes the devices particularly suitable for the wireless communications, defence and industrial markets, including high bandwidth applications such as remote radio head (RRH) and active antennae, test and measurement equipment, software defined radios, massive MIMO and small cells.

“PolarFire FPGA’s transceivers and our JESD204B IP enabled us to successfully perform a loop back demonstration quickly with Analog Devices’ AD9371 transceivers, validating their compatibility for customers looking to leverage the attractive capabilities of both devices,” said Govind Krishnan, director of applications in Microsemi’s Programmable business unit. “Customers who purchase a gold or platinum Libero software licence from Microsemi will also have access to our JESD204B transmit and JESD204B receive IP cores for their designs, offering ease of use for customers utilizing PolarFire with AD9371.”

Microsemi offers a reference design for engineers to run the JESD204B Interface on its PolarFire Evaluation Kit using the JESD204B standalone demonstration graphical user interface (GUI) application. The reference design is built using PolarFire’s high-speed transceiver blocks and the CoreJESD204BTX and CoreJESD204BRX IP cores. The reference design and GUI application are available for Microsemi’s Libero SoC PolarFire Design Suite. All customers with a Libero gold (included with kit) or platinum license can access the JESD204B IP cores for no additional fee.

Microsemi’s PolarFire FPGAs are non-volatile FPGAs providing power and cost savings in comparison to SRAM FPGA solutions with 10G transceivers, advanced input/output (I/O), high security and digital signal processor (DSP) capabilities. The devices have embedded, high-speed transceiver blocks that can handle data rates ranging from 250 Mbps to 12.5 Gbps. The transceiver (PF_XCVR) module integrates several functional blocks to support multiple high-speed serial protocols within the FPGA.

Microsemi; www.microsemi.com/design-support/accelerate-ecosystem-partners / www.microsemi.com/products/fpga-soc/fpga/polarfire-fpga

Analog Devices; www.analog.com/AD9371

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News