Dual-core SHARCs, with ARM cores, use 2W for fanless DSP designs

The ADSP-SC57x/2157x processors are part of a high-performance, power-efficient, real-time series that delivers using two enhanced SHARC+ cores and advanced DSP accelerators (FIR, IIR). The ADSP-SC57x/ ADSP-2157x series consume less than 2W, making the new processor line-up more than 5x more power efficient than previous SHARC products and comparable to the ADSP-SC58x/ 2158x SHARC products. This advantage provides leading digital signal processing performance for applications where thermal management sets the limit for power consumption, or where the higher costs and lower reliability of fans cannot be tolerated. Applications include automotive, consumer and professional audio, multi-axis motor control, and energy distribution systems.

Specifically, in this release, the ADSP-21573 in the ADSP-2157x family is designed for applications where a DSP co-processor is exclusively needed and includes two SHARC+ floating-point DSP cores and a peripheral set matched to a DSP core. It is a lower cost derivative to the successful ADSP-SC58x family, and offers 5.4GFLOPs, 1.8GMACS floating-pt SHARC+ DSP performance (2x 450 MHz).

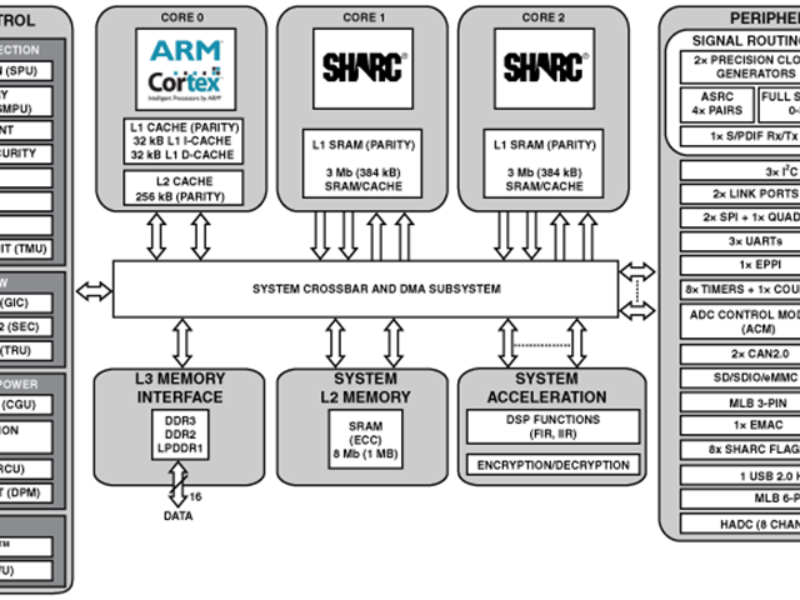

ADSP-SC573 adds an ARM core; the chip has dual-core SHARC+ with 768kB L1 cache, ARM Cortex-A5, 1 MB shared L2 cache, DDR memory interface, Gigabit Ethernet, USB, and SDIO. The ARM core is a standard Cortex-A5 (720 DMIPS at 450 MHz) with FPU and Neon DSP extensions. ADSP-SC572 is s similar spcification but with one SHARC+ core and 384 kB of L1 cache.

ADI’s product page continues;

The code-compatible, enhanced SHARC+ core features clock-rate and power-efficiency improvements and adds instruction/data cache options, native double-precision floating-point support, and a number of other new instructions. Designed for low-power and using a low-leakage CMOS process, the ADSP-SC57x/2157x families deliver 450 MHz with 105°C environments in mind and provide a roadmap to future implementations at higher performance. More than 2 MBytes of fast on-chip SRAM and a DDR3/2/LP interface aid efficient real-time performance while the memory subsystem includes major enhancements with advanced DMA engines for simultaneous data transfer.

ARM TrustZone®security and an onboard crypto hardware accelerators are included for software IP protection. For applications where reliability is a critical requirement, memory parity and error-correction hardware provide higher data integrity.

The ADSP-SC57x/2157x is supported by ADI’s Crosscore Embedded Studio development tool suite, providing design engineers with interactive, real-time development tools that help optimize their design. ADI and Micrium have collaborated to offer µC/OS-II & µC/OS-III real-time kernels on SHARC+.

Analog Devices; www.analog.com

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News