16nm FinFET+ Speedcore eFPGA technology validated for production

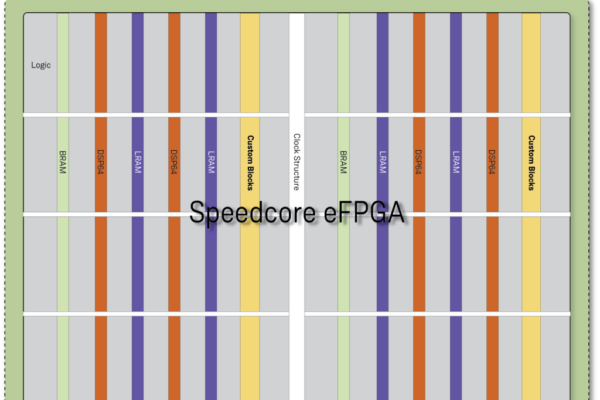

The company performed a full range of bench and ATE tests across a full range of operating conditions to verify the Speedcore chip’s full functionality. Speedcore is a permutable architecture that can scale in size from ten thousand to two million look-up tables. The FPGA architecture fabric works in tandem with large amounts of embedded memory and DSP blocks.

The Speedcore eFPGA technology has been developed as IP to be embedded in SoCs and ASICs to bring reprogrammability to those devices. Achronix claims the eFPGA fabric takes up less die space, performs better, and has lower power and costs than a standalone FPGA. Achronox will configure look-up tables, memory and DSP resources to user specifications, so no resources are wasted.

More information

https://www.achronix.com/product/speedcore/

Related news

Flex Logix: eFPGA IP density, portability and scalability

IP blocks build custom FPGA-hosted algorithms to speed data acceleration

Automotive Qualified Zynq UltraScale+ MPSoC Family now available

SmartFusion2 Maker Board now available globally from Digi-Key

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News